ASSIGNMENT OF ASSIGNORS INTEREST (SEE DOCUMENT FOR DETAILS). Google has not performed a legal analysis and makes no representation as to the accuracy of the date listed.) Filing date Publication date Priority to US10/929,528 priority Critical patent/US6970113B1/en Application filed by Agilent Technologies Inc filed Critical Agilent Technologies Inc Assigned to AGILENT TECHNOLOGIES, INC. Original Assignee Agilent Technologies Inc Priority date (The priority date is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation or warranty as to the accuracy of the list.) Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.) Active, expires Application number US10/929,528 Inventor Ngee Ching Peter Lim Yu Zhou Current Assignee (The listed assignees may be inaccurate.

2 bit gray code counter verilog code pdf#

Google Patents Method for generation of even numbered reduced gray codesĭownload PDF Info Publication number US6970113B1 US6970113B1 US10/929,528 US92952804A US6970113B1 US 6970113 B1 US6970113 B1 US 6970113B1 US 92952804 A US92952804 A US 92952804A US 6970113 B1 US6970113 B1 US 6970113B1 Authority US United States Prior art keywords many entries code gray code bits Prior art date Legal status (The legal status is an assumption and is not a legal conclusion.

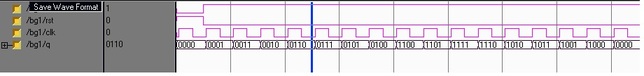

Google Patents US6970113B1 - Method for generation of even numbered reduced gray codes Note : Follow this link to online simulate this design.US6970113B1 - Method for generation of even numbered reduced gray codes $time,reset,load,ud,data,count) end endmodule :counter_tbĮxpected Output : time=0,reset=1,load=x,ud=x,data= 8,count= x Initial begin $monitor("time=%0d,reset=%b,load=%b,ud=%b,data=%d,count=%d", monitor all the input and output ports at times when any inputs changes its state Initial begin clk = 1'b0 repeat(30) #3 clk= ~clk end always block will be executed at each and every positive edge of the clk) begin if(reset) //Set Counter to ZeroĮlse if(load) //load the counter with data value Module counter(clk,reset,up_down,load,data,count) The counter will count up when the “ up_down” signal is logic high, otherwise count down.ĭesign – // Here we will learn to write a verilog HDL to design a 4 bit counter.The counter will be loaded with “ data” input when the “ load” signal is at logic high.The Counter will be set to Zero when “ reset” input is at logic high.The counter (“ count“) value will be evaluated at every positive (rising) edge of the clock (“ clk“) cycle.Code Converters - BCD(8421) to/from Excess-3.Design 101 sequence detector (Mealy machine).Code Converters - Binary to/from Gray Code.Difference between combinational and sequential circuit.Flip-flop types, their Conversion and Applications.Difference between Unipolar, Polar and Bipolar Line Coding Schemes.

2 bit gray code counter verilog code full#

0 kommentar(er)

0 kommentar(er)